SBOS019A - JANUARY 1992 - SEPTEMBER 2003

# **FET-Input, Low Distortion OPERATIONAL AMPLIFIER**

# **FEATURES**

● LOW DISTORTION: 0.0003% at 1kHz

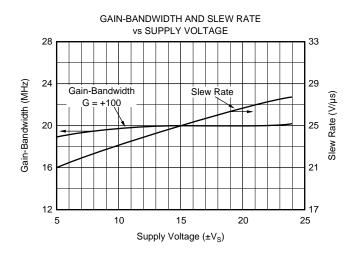

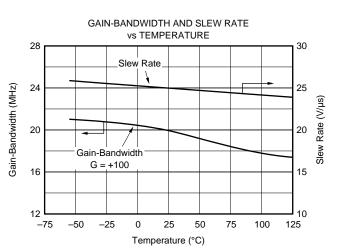

● LOW NOISE: 10nV/√Hz ● HIGH SLEW RATE: 25V/μs

WIDE GAIN-BANDWIDTH: 20MHz

• UNITY-GAIN STABLE

• WIDE SUPPLY RANGE:  $V_s = \pm 4.5$  to  $\pm 24V$

DRIVES 600Ω LOAD

DUAL VERSION AVAILABLE (OPA2604)

### DESCRIPTION

The OPA604 is a FET-input operational amplifier designed for enhanced AC performance. Very low distortion, low noise and wide bandwidth provide superior performance in high quality audio and other applications requiring excellent dynamic performance.

New circuit techniques and special laser trimming of dynamic circuit performance yield very low harmonic distortion. The result is an op amp with exceptional sound quality. The lownoise FET input of the OPA604 provides wide dynamic range, even with high source impedance. Offset voltage is laser-trimmed to minimize the need for interstage coupling

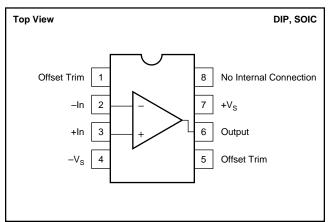

The OPA604 is available in 8-pin plastic mini-DIP and SO-8 surface-mount packages, specified for the -25°C to +85°C temperature range.

### APPLICATIONS

- PROFESSIONAL AUDIO EQUIPMENT

- **PCM DAC I/V CONVERTERS**

- SPECTRAL ANALYSIS EQUIPMENT

- ACTIVE FILTERS

- TRANSDUCER AMPLIFIERS

- **DATA ACQUISITION**

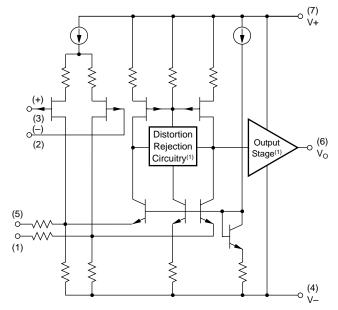

NOTE: (1) Patents Granted: #5053718, 5019789

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### **ABSOLUTE MAXIMUM RATINGS**

| Power Supply Voltage                 | ±25V               |

|--------------------------------------|--------------------|

| Input Voltage                        | (V–)–1V to (V+)+1V |

| Output Short Circuit to Ground       | Continuous         |

| Operating Temperature                | –40°C to +100°C    |

| Storage Temperature                  | 40°C to +125°C     |

| Junction Temperature                 | +150°C             |

| Lead Temperature (soldering, 10s) AP | +300°C             |

| Lead Temperature (soldering, 3s) AU  | +260°C             |

#### **PIN CONFIGURATION**

Any integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet published specifications.

#### PACKAGE/ORDERING INFORMATION

For the most current package and ordering information, see to the Package Option Addendum at the end of this data sheet.

# **ELECTRICAL CHARACTERISTICS**

$T_A$  = +25°C,  $V_S$  = ±15V, unless otherwise noted.

| PARAMETER                                                                                                                                                                           | CONDITION                                                                           | MIN        | TYP                                             | MAX         | UNITS                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------|-------------------------------------------------|-------------|--------------------------------------------------------------------|

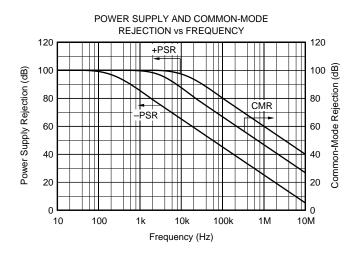

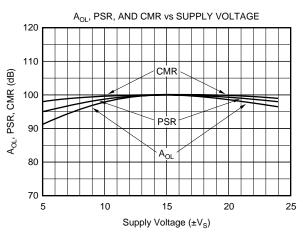

| OFFSET VOLTAGE Input Offset Voltage Average Drift Power Supply Rejection                                                                                                            | V <sub>S</sub> = ±5 to ±24V                                                         | 80         | ±1<br>±8<br>100                                 | ±5          | mV<br>μV/°C<br>dB                                                  |

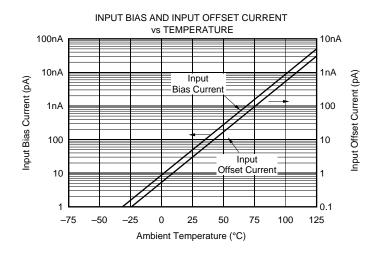

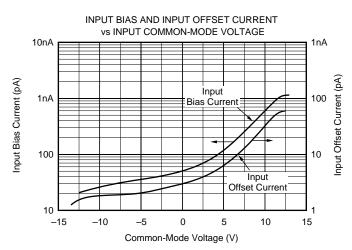

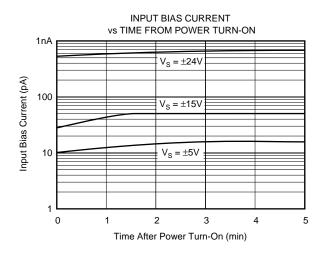

| INPUT BIAS CURRENT <sup>(1)</sup> Input Bias Current Input Offset Current                                                                                                           | $V_{CM} = 0V$ $V_{CM} = 0V$                                                         |            | 50<br>±3                                        |             | pA<br>pA                                                           |

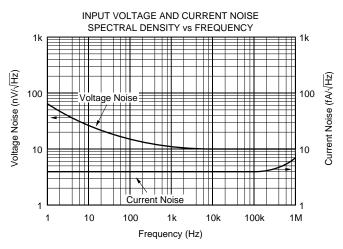

| NOISE Input Voltage Noise Noise Density: f = 10Hz f = 100Hz f = 10Hz f = 10kHz Voltage Noise, BW = 20Hz to 20kHz Input Bias Current Noise Current Noise Density, f = 0.1Hz to 20kHz |                                                                                     |            | 25<br>15<br>11<br>10<br>1.5                     |             | nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>μV <sub>PP</sub><br>fA/√Hz |

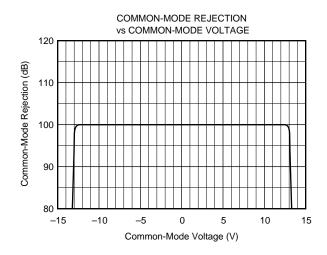

| INPUT VOLTAGE RANGE Common-Mode Input Range Common-Mode Rejection                                                                                                                   | V <sub>CM</sub> = ±12V                                                              | ±12<br>80  | ±13<br>100                                      |             | V<br>dB                                                            |

| INPUT IMPEDANCE Differential Common-Mode                                                                                                                                            |                                                                                     |            | 10 <sup>12</sup>    8<br>10 <sup>12</sup>    10 |             | Ω    pF<br>Ω    pF                                                 |

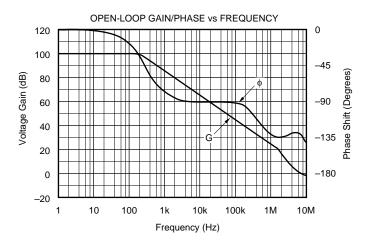

| OPEN-LOOP GAIN Open-Loop Voltage Gain                                                                                                                                               | $V_O = \pm 10V, R_L = 1k\Omega$                                                     | 80         | 100                                             |             | dB                                                                 |

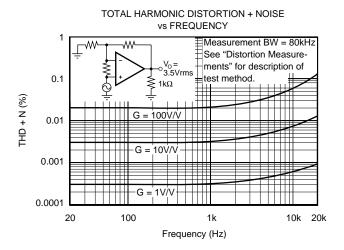

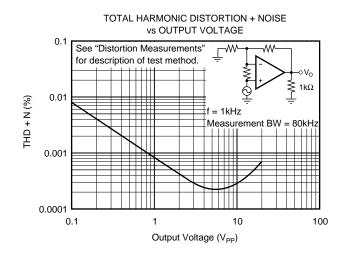

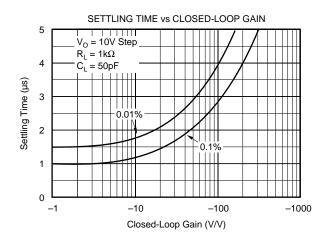

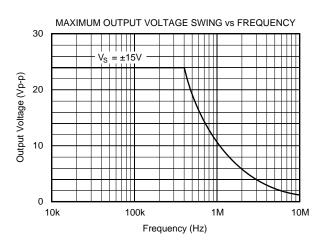

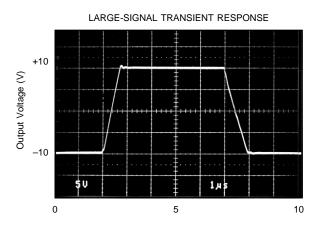

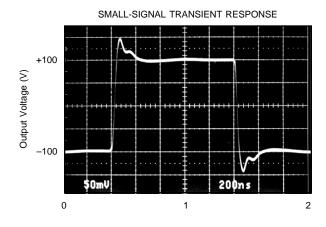

| FREQUENCY RESPONSE Gain-Bandwidth Product Slew Rate Settling Time: 0.01% 0.1% Total Harmonic Distortion + Noise (THD+N)                                                             | $G = 100$ $20V_{PP}, R_{L} = 1k\Omega$ $G = -1, 10V \text{ Step}$ $G = 1, f = 1kHz$ | 15         | 20<br>25<br>1.5<br>1<br>0.0003                  |             | MHz<br>V/μs<br>μs<br>μs<br>%                                       |

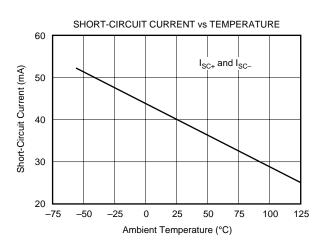

| OUTPUT Voltage Output Current Output Short Circuit Current Output Resistance, Open-Loop                                                                                             | $V_O = 3.5 V rms, R_L = 1 k\Omega$ $R_L = 600\Omega$ $V_O = \pm 12 V$               | ±11        | ±12<br>±35<br>±40<br>25                         |             | V<br>mA<br>mA                                                      |

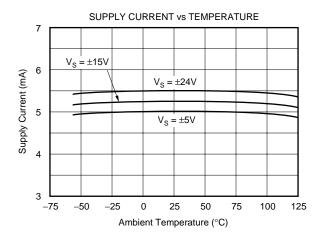

| POWER SUPPLY Specified Operating Voltage Operating Voltage Range Current                                                                                                            |                                                                                     | ±4.5       | ±15<br>±5.3                                     | ±24<br>±7   | V<br>V<br>mA                                                       |

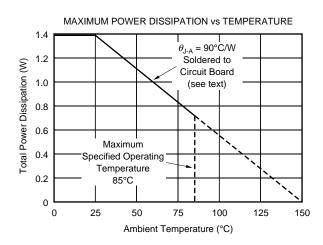

| <b>TEMPERATURE RANGE</b> Specification Storage Thermal Resistance <sup>(2)</sup> , $\theta_{\rm JA}$                                                                                |                                                                                     | -25<br>-40 | 90                                              | +85<br>+125 | °C<br>°C<br>°C                                                     |

NOTES: (1) Typical performance, measured fully warmed-up. (2) Soldered to circuit board—see text.

# TYPICAL CHARACTERISTICS

$T_{\Delta}$  = +25°C,  $V_{S}$  = ±15V, unless otherwise noted.

# TYPICAL CHARACTERISTICS (Cont.)

$T_A = +25$ °C,  $V_S = \pm 15$ V, unless otherwise noted.

# **TYPICAL CHARACTERISTICS (Cont.)**

$T_A = +25$ °C,  $V_S = \pm 15$ V, unless otherwise noted.

# TYPICAL CHARACTERISTICS (Cont.)

$T_A = +25$ °C,  $V_S = \pm 15$ V, unless otherwise noted.

## **APPLICATIONS INFORMATION**

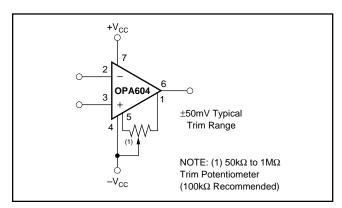

#### **OFFSET VOLTAGE ADJUSTMENT**

The OPA604 offset voltage is laser-trimmed and will require no further trim for most applications. As with most amplifiers, externally trimming the remaining offset can change drift performance by about  $0.3\mu V/^{\circ}C$  for each  $100\mu V$  of adjusted offset. The OPA604 can replace many other amplifiers by leaving the external null circuit unconnected.

The OPA604 is unity-gain stable, making it easy to use in a wide range of circuitry. Applications with noisy or high impedance power supply lines may require decoupling capacitors close to the device pins. In most cases, a  $1\mu F$  tantalum capacitor at each power supply pin is adequate.

FIGURE 1. Offset Voltage Trim.

#### **DISTORTION MEASUREMENTS**

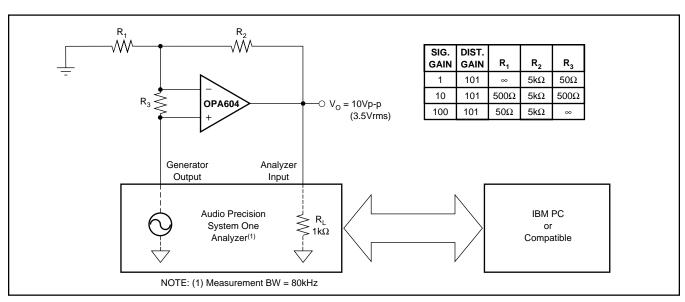

The distortion produced by the OPA604 is below the measurement limit of virtually all commercially available equipment. A special test circuit, however, can be used to extend the measurement capabilities.

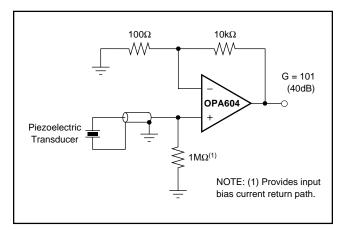

Op amp distortion can be considered an internal error source which can be referred to the input. Figure 2 shows a circuit which causes the op amp distortion to be 101 times greater than normally produced by the op amp. The addition of  $R_3$  to the otherwise standard noninverting amplifier configuration alters the feedback factor or noise gain of the circuit. The closed-loop gain is unchanged, but the feedback available for error correction is reduced by a factor of 101. This extends the measurement limit, including the effects of the signal-source purity, by a factor of 101. Note that the input signal and load applied to the op amp are the same as with conventional feedback without  $R_3$ .

Validity of this technique can be verified by duplicating measurements at high gain and/or high frequency where the distortion is within the measurement capability of the test equipment. Measurements for this data sheet were made with the Audio Precision System One, which greatly simplifies such repetitive measurements. The measurement technique can, however, be performed with manual distortion measurement instruments.

#### **CAPACITIVE LOADS**

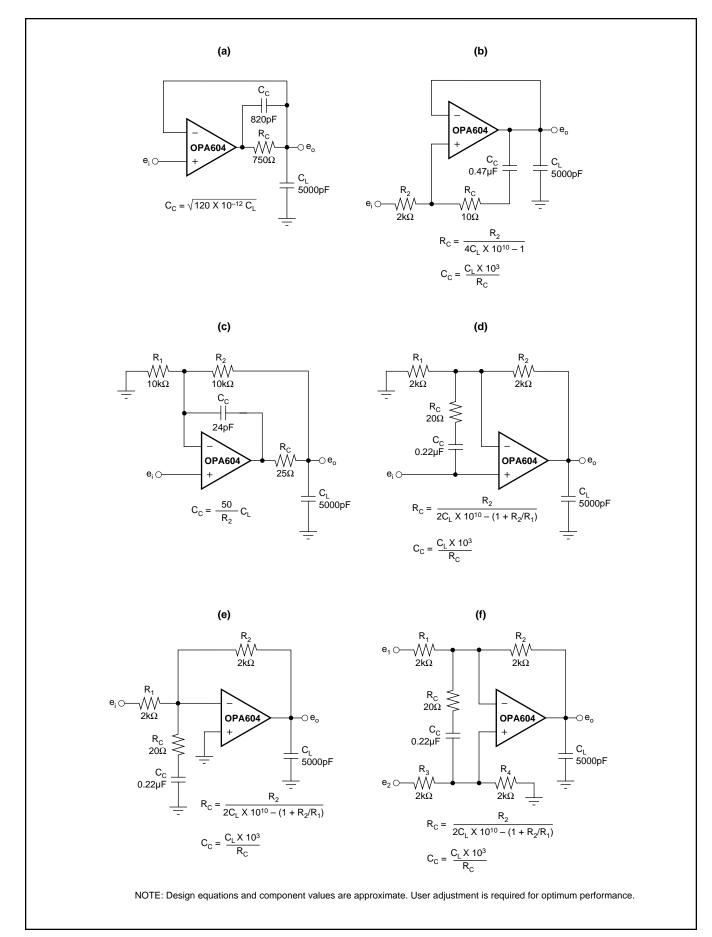

The dynamic characteristics of the OPA604 have been optimized for commonly encountered gains, loads and operating conditions. The combination of low closed-loop gain and capacitive load will decrease the phase margin and may lead to gain peaking or oscillations. Load capacitance reacts with the op amp's open-loop output resistance to form an additional pole in the feedback loop. Figure 3 shows various circuits which preserve phase margin with capacitive load. For details of analysis techniques and applications circuits, refer to application bulletin AB-028 (SBOA015) located at www.ti.com.

For the unity-gain buffer, Figure 3a, stability is preserved by adding a phase-lead network,  $R_{\text{C}}$  and  $C_{\text{C}}$ . Voltage drop across  $R_{\text{C}}$  will reduce output voltage swing with heavy loads. An alternate circuit, Figure 3b, does not limit the output with low load impedance. It provides a small amount of positive feedback to reduce the net feedback factor. Input impedance of this circuit falls at high frequency as op amp gain rolloff reduces the bootstrap action on the compensation network.

Figures 3c and 3d show compensation techniques for noninverting amplifiers. Like the follower circuits, the circuit in Figure 3d eliminates voltage drop due to load current, but at the penalty of somewhat reduced input impedance at high frequency.

Figures 3e and 3f show input lead compensation networks for inverting and difference amplifier configurations.

#### **NOISE PERFORMANCE**

Op amp noise is described by two parameters—noise voltage and noise current. The voltage noise determines the noise performance with low source impedance. Low noise bipolar-input op amps such as the OPA27 and OPA37 provide very low voltage noise. But if source impedance is greater than a few thousand ohms, the current noise of

bipolar-input op amps react with the source impedance and will dominate. At a few thousand ohms source impedance and above, the OPA604 will generally provide lower noise.

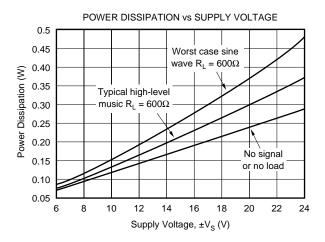

#### POWER DISSIPATION

The OPA604 is capable of driving a  $600\Omega$  load with power-supply voltages up to  $\pm 24$ V. Internal power dissipation is increased when operating at high power supply voltage. The typical characteristic curve, Power Dissipation vs Power Supply Voltage, shows quiescent dissipation (no signal or no load) as well as dissipation with a worst case continuous sine wave. Continuous high-level music signals typically produce dissipation significantly less than worst-case sine waves.

Copper leadframe construction used in the OPA604 improves heat dissipation compared to conventional plastic packages. To achieve best heat dissipation, solder the device directly to the circuit board and use wide circuit board traces

#### **OUTPUT CURRENT LIMIT**

Output current is limited by internal circuitry to approximately ±40mA at 25°C. The limit current decreases with increasing temperature as shown in the typical curves.

FIGURE 2. Distortion Test Circuit.

FIGURE 3. Driving Large Capacitive Loads.

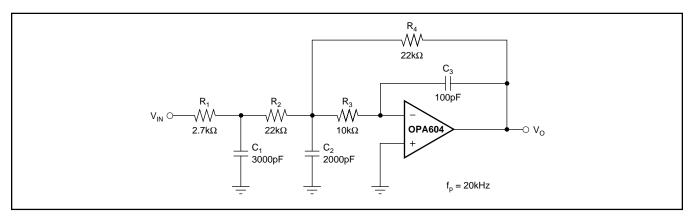

FIGURE 4. Three-Pole Low-Pass Filter.

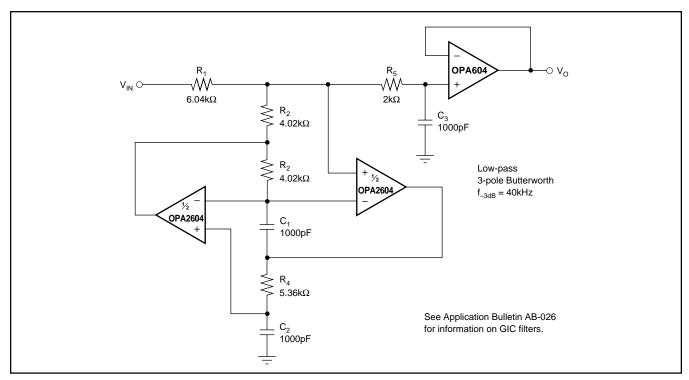

FIGURE 5. Three-Pole Generalized Immittance Converter (GIC) Low-Pass Filter.

FIGURE 6. Differential Amplifier with Low-Pass Filter.

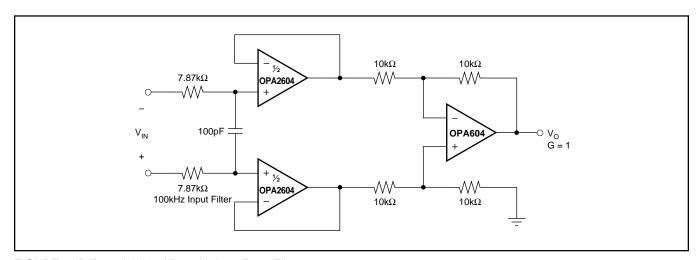

FIGURE 7. High Impedance Amplifier.

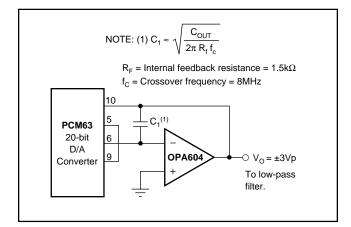

FIGURE 8. Digital Audio DAC I-V Amplifier.

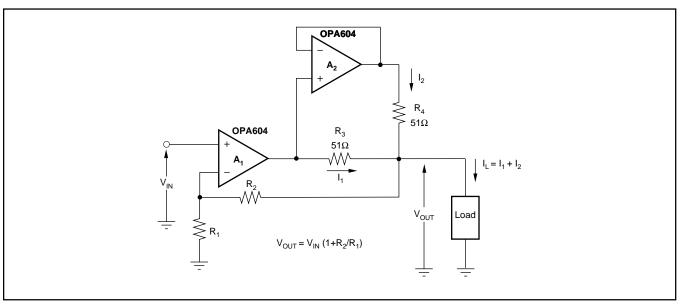

FIGURE 9. Using Two OPA604 Op Amps to Double the Output Current to a Load.

## **SOUND QUALITY**

The following discussion is provided, recognizing that not all measured performance behavior explains or correlates with listening tests by audio experts. The design of the OPA604 included consideration of both objective performance measurements, as well as an awareness of widely held theory on the success and failure of previous op amp designs.

#### **SOUND QUALITY**

The sound quality of an op amp is often the crucial selection criteria—even when a data sheet claims exceptional distortion performance. By its nature, sound quality is subjective. Furthermore, results of listening tests can vary depending on application and circuit configuration. Even experienced listeners in controlled tests often reach different conclusions.

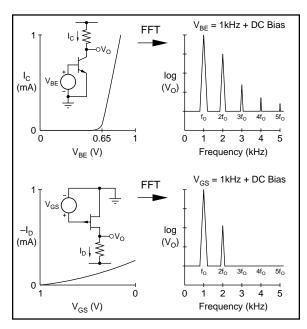

Many audio experts believe that the sound quality of a high performance FET op amp is superior to that of bipolar op amps. A possible reason for this is that bipolar designs generate greater odd-order harmonics than FETs. To the human ear, odd-order harmonics have long been identified as sounding more unpleasant than even-order harmonics. FETs, like vacuum tubes, have a square-law I-V transfer function which is more linear than the exponential transfer function of a bipolar transistor. As a direct result of this square-law characteristic, FETs produce predominantly even-order harmonics. Figure 10 shows the transfer function of a bipolar transistor and FET. Fourier transformation of both transfer functions reveals the lower odd-order harmonics of the FET amplifier stage.

FIGURE 10. I-V and Spectral Response of NPN and JFET.

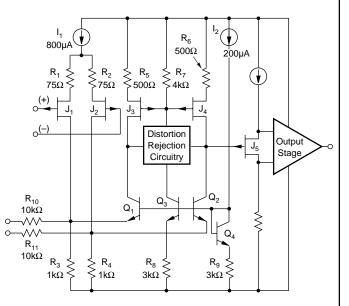

#### THE OPA604 DESIGN

The OPA604 uses FETs throughout the signal path, including the input stage, input-stage load, and the important phase-splitting section of the output stage. Bipolar transistors are used where their attributes, such as current capability are important, and where their transfer characteristics have minimal impact.

The topology consists of a single folded-cascode gain stage followed by a unity-gain output stage. Differential input transistors  $J_1$  and  $J_2$  are special large-geometry, P-channel JFETs. Input stage current is a relatively high  $800\mu A$ , providing high transconductance and reducing voltage noise. Laser trimming of stage currents and careful attention to symmetry yields a nearly symmetrical slew rate of  $\pm 25 V/\mu s$ .

The JFET input stage holds input bias current to approximately 50pA or roughly 3000 times lower than common bipolar-input audio op amps. This dramatically reduces noise with high-impedance circuitry.

The drains of  $J_1$  and  $J_2$  are cascoded by  $Q_1$  and  $Q_2$ , driving the input stage loads, FETs  $J_3$  and  $J_4$ . Distortion reduction circuitry (patented) linearizes the open-loop response and increases voltage gain. The 20MHz bandwidth of the OPA604 further reduces distortion through the user-connected feedback loop.

The output stage consists of a JFET phase-splitter loaded into high speed all-NPN output drivers. Output transistors are biased by a special circuit to prevent cutoff, even with full output swing into  $600\Omega$  loads.

6-Sep-2016

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing |   | Package<br>Qty | Eco Plan                   | Lead/Ball Finish (6) | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|---|----------------|----------------------------|----------------------|---------------------|--------------|-------------------------|---------|

| OPA604AP         | ACTIVE | PDIP         | Р                  | 8 | 50             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | N / A for Pkg Type  | -40 to 85    | OPA604AP                | Samples |

| OPA604APG4       | ACTIVE | PDIP         | Р                  | 8 | 50             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | N / A for Pkg Type  | -40 to 85    | OPA604AP                | Samples |

| OPA604AU         | ACTIVE | SOIC         | D                  | 8 | 75             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-3-260C-168 HR | -40 to 85    | OPA<br>604AU            | Samples |

| OPA604AU/2K5     | ACTIVE | SOIC         | D                  | 8 | 2500           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-3-260C-168 HR | -40 to 85    | OPA<br>604AU            | Samples |

| OPA604AU/2K5G4   | ACTIVE | SOIC         | D                  | 8 | 2500           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-3-260C-168 HR | -40 to 85    | OPA<br>604AU            | Samples |

| OPA604AUE4       | ACTIVE | SOIC         | D                  | 8 | 75             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-3-260C-168 HR | -40 to 85    | OPA<br>604AU            | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

### **PACKAGE OPTION ADDENDUM**

6-Sep-2016

(6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2013

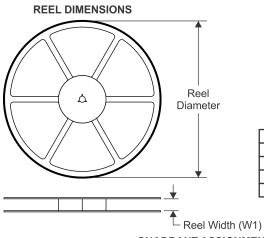

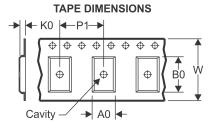

### TAPE AND REEL INFORMATION

| Α0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

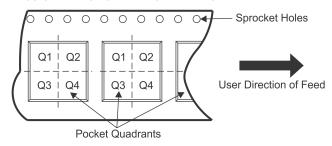

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |   |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA604AU/2K5 | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2013

#### \*All dimensions are nominal

| ĺ | Device       | Package Type | Package Drawing Pins SP |   |      | Length (mm) | Width (mm) | Height (mm) |  |

|---|--------------|--------------|-------------------------|---|------|-------------|------------|-------------|--|

|   | OPA604AU/2K5 | SOIC         | D                       | 8 | 2500 | 367.0       | 367.0      | 35.0        |  |

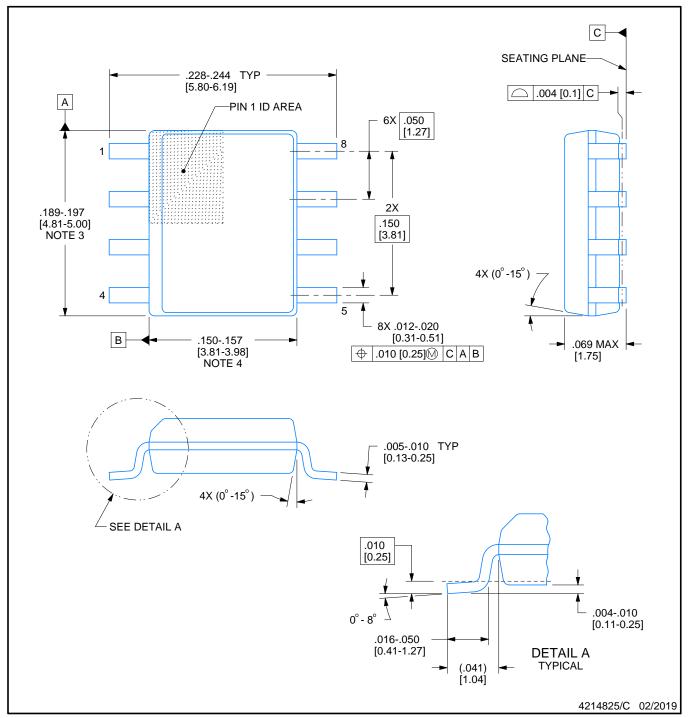

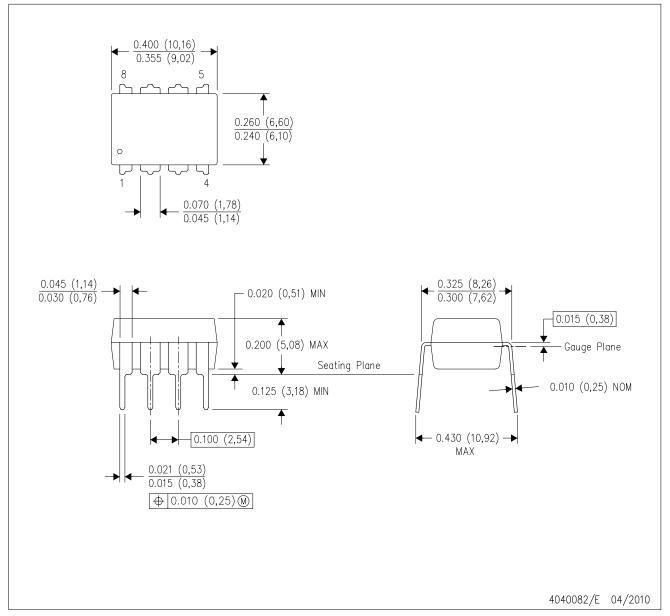

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

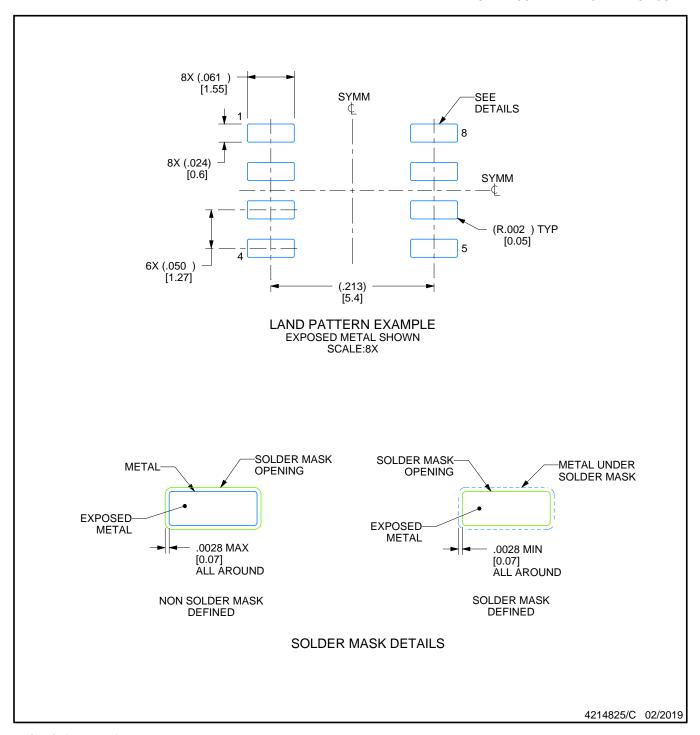

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

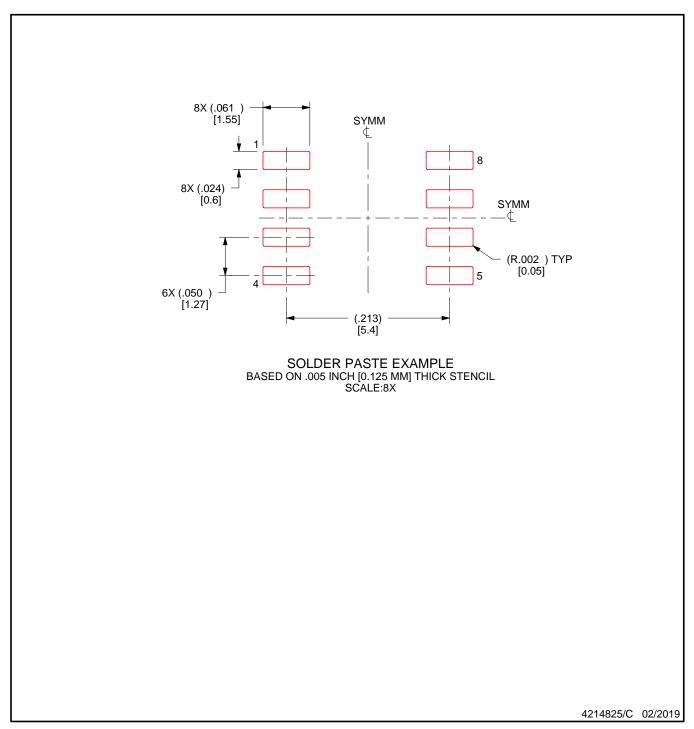

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# P (R-PDIP-T8)

## PLASTIC DUAL-IN-LINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001 variation BA.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated